PROCESSOR OPERATING MANUAL

# **OPERATING MANUAL**

# **OPERATING MANUAL**

RADIO CORPORATION OF AMERICA 70-45-401

August 1966

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

왕 [11] 왕 남, 가 갔다. 왕 소리는 것 봄 소]**::**은 가격한 전 것이는 것을 하는 것이 같은 것이 있다. 것이 같은 것이 있는 것이 있다.

First Printing: August, 1966

# CONTENTS

|             | F                                   | Page      |

|-------------|-------------------------------------|-----------|

| DESCRIPTION | General                             | 1         |

|             | Functional                          | 1         |

|             | Processor States                    | 1         |

|             | Organization of Data                | <b>2</b>  |

|             | Data Format                         | 2         |

|             | Numbering Systems                   | 2         |

|             | Instructions                        | 4         |

|             | Addressing Main Memory              | 4         |

|             | Input/Output Control                | 7         |

|             | Sub-Units                           | 8         |

|             | Basic Processing Unit               | 8         |

|             | Main Memory                         | 8         |

|             | Non-Addressable Memory              | 8         |

|             | Fast Memory                         | 8         |

|             | Read-Only Memory                    | 13        |

|             | Program Control and Arithmetic Unit | 13        |

|             | Operator's Console                  | 14        |

|             | Maintenance Console Panel           | 15        |

|             | Power Supply                        | 16        |

|             | Controls and Indicators             | 16        |

|             | Power Supply Panels                 | 16        |

|             | Operator's Console Display Panel    | 19        |

|             | Operator's Keyboard                 | 22        |

|             | Maintenance Console Panels          | 23        |

|             | Features                            | 33        |

|             | Interrupt                           | 33        |

|             | Accuracy Control                    | <b>34</b> |

|             | Optional Features                   | 36        |

|             | Memory Protect                      | 36        |

|             | Elapsed Time Clock                  | 36        |

|             | Direct Control                      | 36        |

|             | Selector Channels                   | 36        |

|             | Emulator Options                    | 36        |

| OPERATION   | Preparation for Operation           | 37        |

|             | Operator's Console                  | 37        |

|             | Power Supply Rack                   | 37        |

|             | Normal Operation                    | 37        |

|             | Applying Power                      | 37        |

|             | Removing Power                      | 37        |

|             | Initial Program Loading             | 38        |

|             | Error Recovery                      | 42        |

|             |                                     |           |

# OPERATION (Cont'd)

# CONTENTS (Cont'd)

|               | P                                                                                                                      | age                  |

|---------------|------------------------------------------------------------------------------------------------------------------------|----------------------|

|               | Special Operations       Manual Initiation of I/O         ROM Check       Writing to Consecutive Main Memory Locations | 49<br>49<br>50<br>51 |

|               | Reading from Consecutive Main Memory Locations                                                                         | 51                   |

|               | Writing to Consecutive Fast Memory Locations                                                                           | 51                   |

|               | Reading from Consecutive Fast Memory Locations                                                                         | 52                   |

|               | Equipment Care                                                                                                         | 53                   |

|               | General                                                                                                                | 53                   |

|               | Inspection                                                                                                             | 53                   |

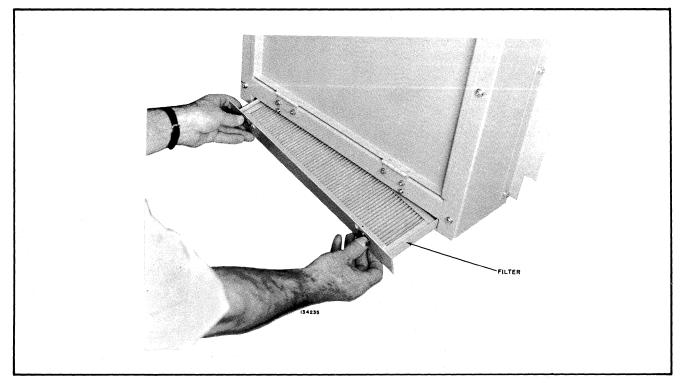

|               | Filters                                                                                                                | 54                   |

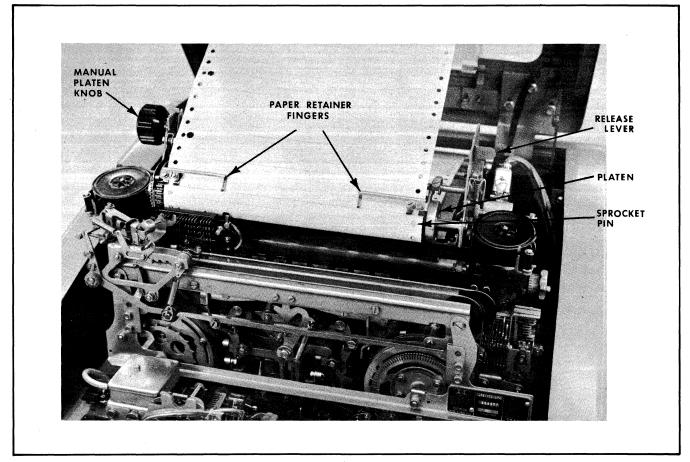

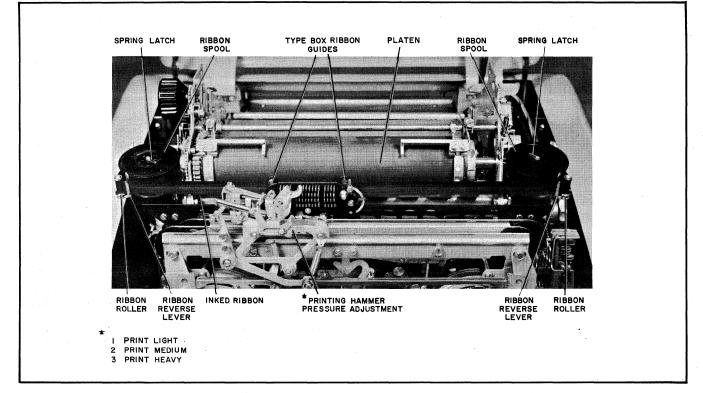

|               | Loading Paper<br>Pibbon Poplacement                                                                                    | 54<br>56             |

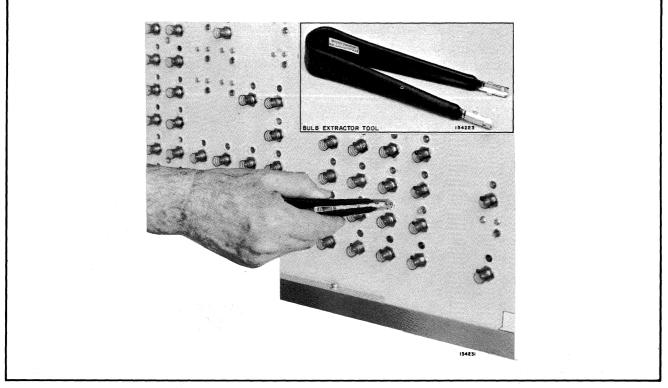

|               | Ribbon ReplacementLamp Replacement                                                                                     | 50<br>58             |

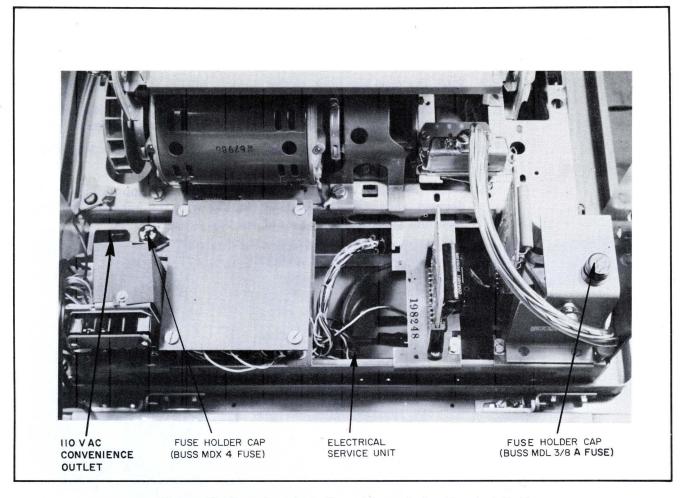

|               | Fuse Replacement                                                                                                       | 58                   |

|               | Cleaning the Type Pallets                                                                                              | <b>6</b> 0           |

|               | Cleaning the Platen                                                                                                    | 60                   |

| LIST OF       | Frontispiece — Model 70/45 Processor and Model 70/97 Operator's                                                        |                      |

| ILLUSTRATIONS | Console<br>Figure 1. Data Formats                                                                                      | vi<br>3              |

|               | Figure 2. 70/45 Instruction Formats                                                                                    | э<br>5               |

|               | Figure 3. 70/45 Input/Output Flow                                                                                      | 7                    |

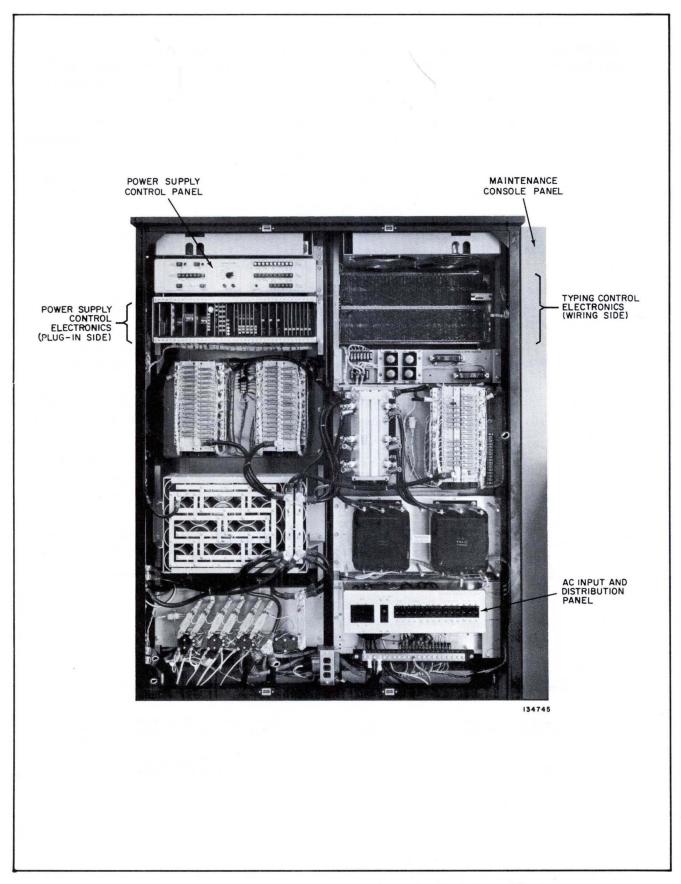

|               | Figure 4. Interior Model 70/45 Processor (Rear View Showing<br>Frame Opened)                                           | 9                    |

|               | Figure 5. Interior Model 70/45 Processor (Rear View Showing<br>Frame Closed)                                           | 10                   |

|               | Figure 6. Operator's Console (Model 70/97)                                                                             | 14                   |

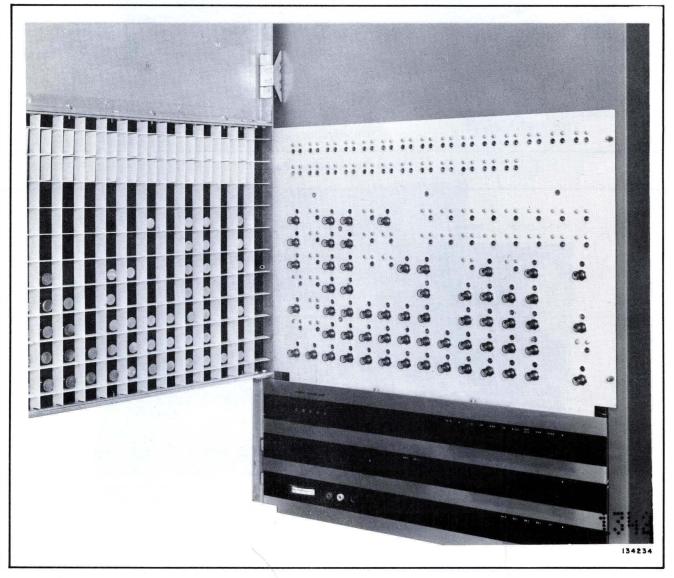

|               | Figure 7. Model 70/45 Maintenance Console Panel (Showing Main-<br>tenance and Auxiliary Panels)                        | 15                   |

|               | Figure 8. AC Input and Distribution Panel                                                                              | 16                   |

|               | Figure 9. Power Supply and Control Electronics Rack (Rear View)                                                        | 17                   |

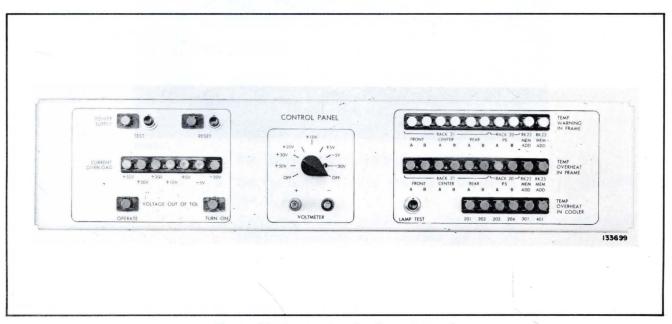

|               | Figure 10. Power Supply Control Panel                                                                                  | 18                   |

|               | Figure 11. Model 70/97 Operator's Console Display Panel                                                                | 19                   |

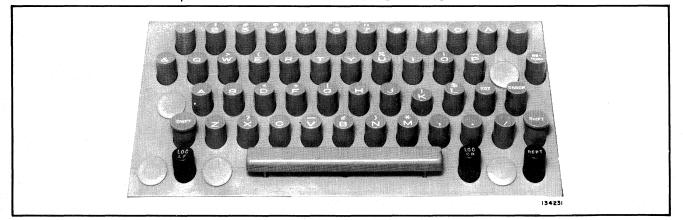

|               | Figure 12. Model 70/97 Operator's Console Keyboard Layout                                                              | 22                   |

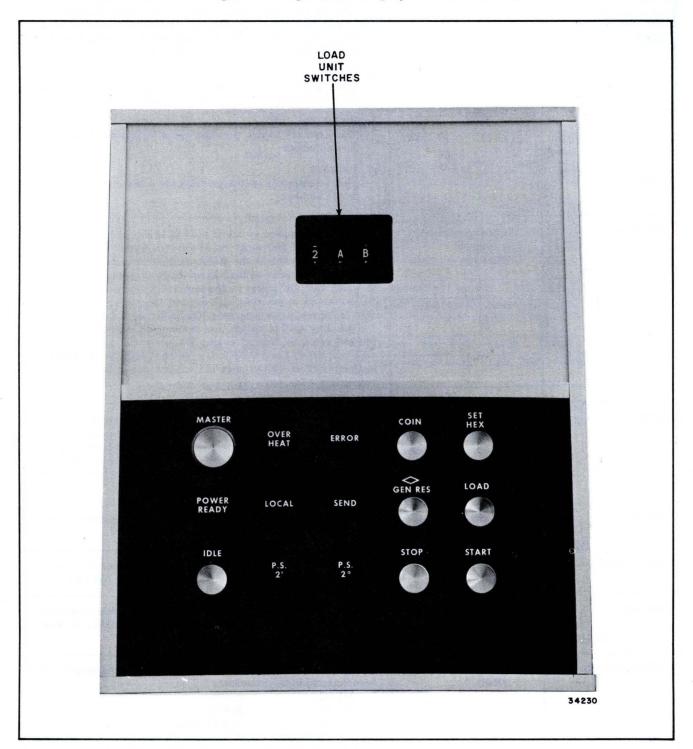

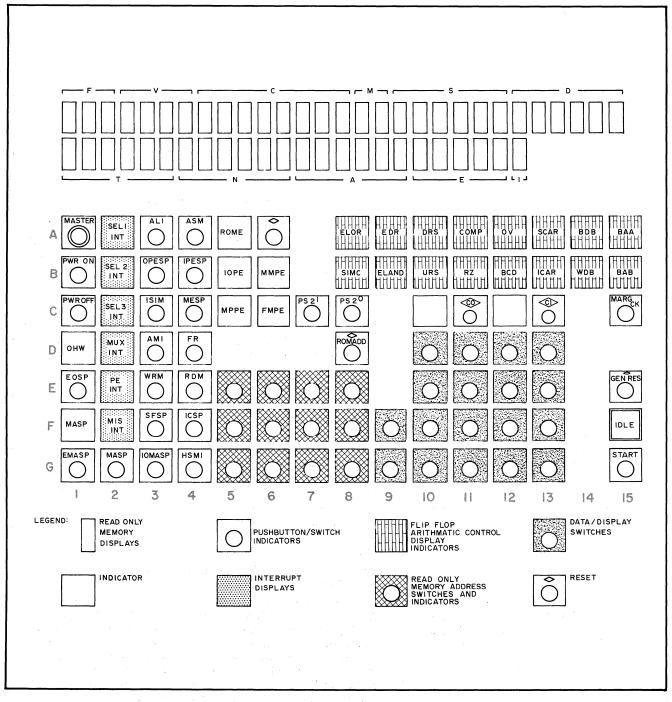

|               | Figure 13. Model 70/45 Maintenance Panel                                                                               | 23                   |

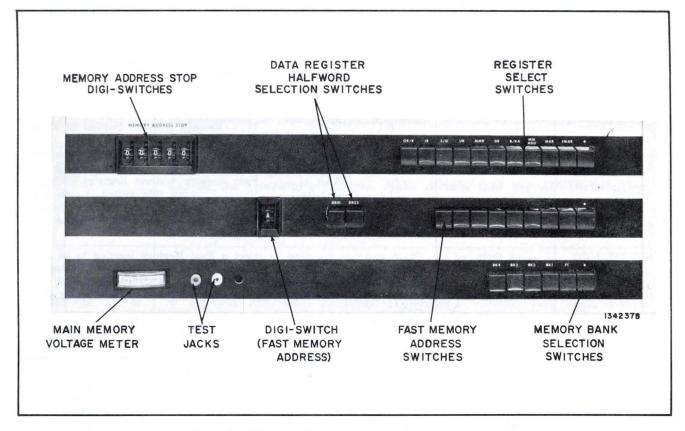

|               | Figure 14. Model 70/45 Auxiliary Maintenance Panel                                                                     | 31                   |

|               | Figure 15. Removing Filters                                                                                            | 53                   |

|               | Figure 16. Loading Paper                                                                                               | 55                   |

|               | Figure 17. Ribbon Replacement                                                                                          | 55<br>56             |

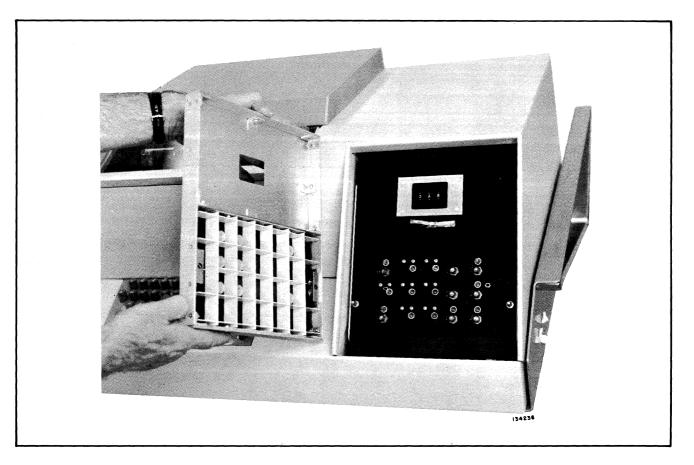

|               | Figure 18. Interior View of 70/45 Processor Maintenance Panel                                                          | 56<br>57             |

|               | Figure 19. Removal of Operator's Display Panel CoverFigure 20. Light Bulb Replacement                                  | 57<br>57             |

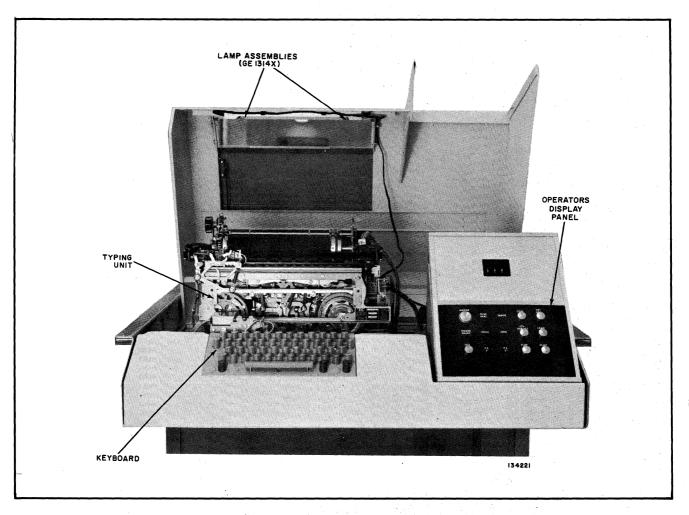

|               | Figure 21. 70/97 Operator Console (Top Cover Ass'y Raised)                                                             | 58                   |

|               | Figure 22. Fuse Locations (Rear View of the Electrical Unit)                                                           | 59                   |

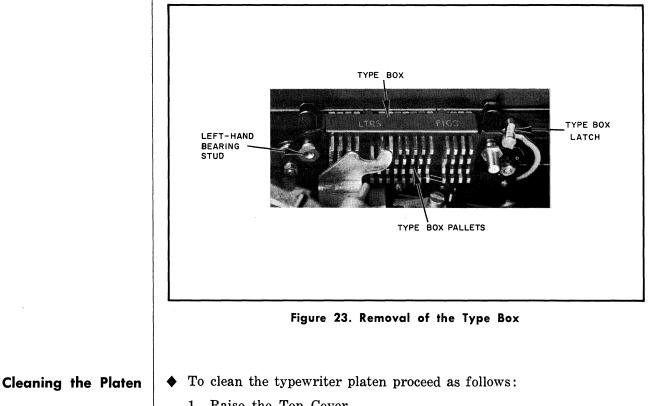

|               | Figure 23. Removal of the Type Box                                                                                     | 60                   |

# CONTENTS (Cont'd)

# Page

| LIST OF    | Table1. Spectra 70/45 Model Numbers1                                                      |

|------------|-------------------------------------------------------------------------------------------|

| TABLES     | Table         2. Basic Hexadecimal Marking System         2                               |

|            | Table         3. Operator's Console Panel (Indicators and Controls)         20            |

|            | Table 4. Model 70/45 Maintenance Panel (Indicators and Controls) 24                       |

|            | Table 5. Model 70/45 Auxiliary Maintenance Panel (Indicators and                          |

|            | Controls) 31                                                                              |

|            | Table         6. Register Addressing in the Processor States         33                   |

|            | Table7. 70/45InterruptConditions35                                                        |

|            | Table8. Summary of Special Operations43                                                   |

|            | Table 9. Conversion Table (FM Address Switches, Hexadecimal                               |

|            | Address) 44                                                                               |

|            | Table 10. Table of Instructions45/46                                                      |

|            | Table 11. Fast Memory Layout and Register Assignment 47/48                                |

| GLOSSARY   |                                                                                           |

| APPENDICES | A — Extended Binary-Coded-Decimal Interchange Code (EBCDIC) . 65                          |

|            | B — American Standard Code for Information Interchange (ASCII)<br>(Extended to 8 Bits) 66 |

|            | C — Character Codes                                                                       |

|            | D — Powers of Two Table 72                                                                |

|            | E — Input/Output Operation Information                                                    |

|            | F — Typewriter Graphics and Codes 74                                                      |

|            |                                                                                           |

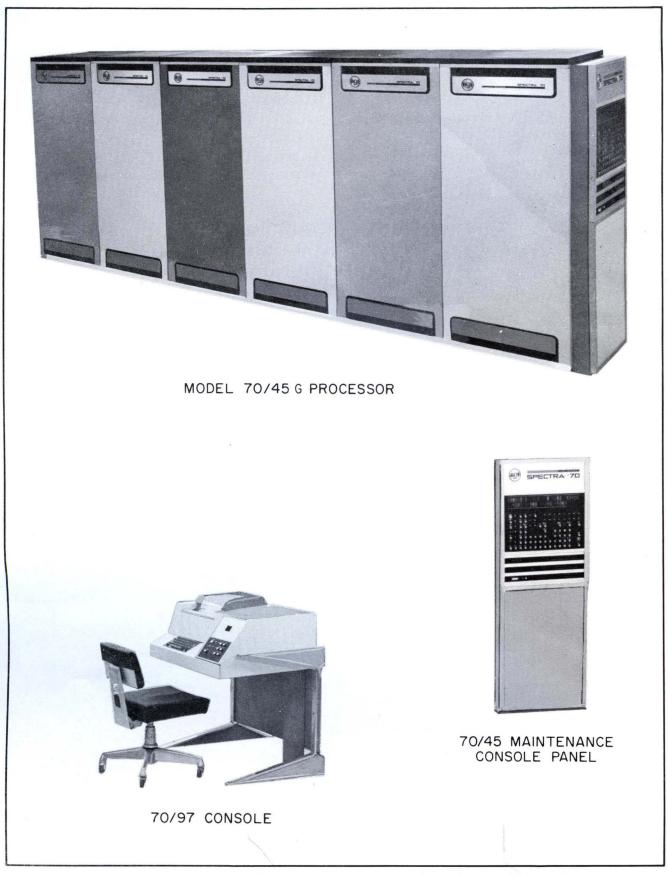

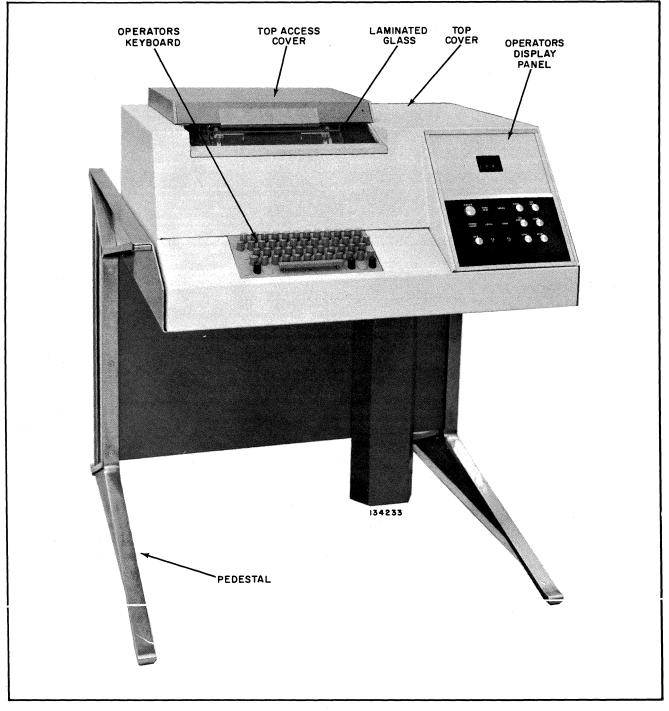

Frontispiece — Model 70/45 Processor and Model 70/97 Operator's Console

## DESCRIPTION

#### **GENERAL**

• The RCA Model 70/45 Processor is a solid state, general purpose, digital processor. It is the main element of a system handling medium-large data processing applications. Because of its storage capacity, and data transmission and computation rates, this processor is applicable to both data processing and scientific-problem solving. The internal logic is controlled by Elementary Operation (EO's) stored in a read-only control memory.

The 70/45 Processor may be any one of the model numbers listed in Table 1. The memory size (capacity in bytes) and number of racks required to accommodate these sizes are also given in this table. The method of operation is the same for the different models and is described in the Operation portion of this manual.

The 70/45 is a variable-format processor, consisting of a Main Memory, Read-Only Memory, Non-addressable Memory, Fast Memory, Program Control, and Input/Output Control.

| Model<br>Number | Capacity<br>(in bytes) | Rack Number<br>Identification | Remarks                                        |

|-----------------|------------------------|-------------------------------|------------------------------------------------|

| 70/45 C         | 16,384                 | 20 and 21                     | Rack numbers and their                         |

| 70/45 D         | 32,768                 | 20 and 21                     | design functions:                              |

| 70/45 E         | 65,536                 | 20 and 21                     | 20 = Power Supply<br>21 = Basic Processor Unit |

| 70/45 F         | 131,072                | 20, 21, and 22                | 22 = Memory Addition                           |

| 70/45 G         | 262,144                | 20, 21, 22, and 23            | 23 = Memory Addition                           |

| Table 1. Spectra 70/45 Model Numbe |

|------------------------------------|

|------------------------------------|

## FUNCTIONAL

**Processor States**

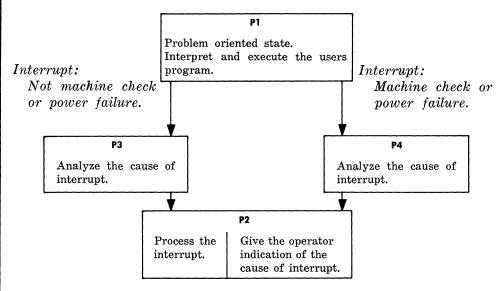

• The RCA 70/45 Processor has four processor states that provide control of system and program interrupts. Programs may be executed in any one of these states, because each state is completely independent and has its own set of registers (except floating point register). The four processor states and their functions are as follows:

- 1. Processor State  $P_1$  normally interprets and executes the user's program. The processing state is the problem-oriented state.

- 2. Processor State  $P_2$  performs specific program tasks as dictated by the Interrupt Control State  $P_3$ .

- 3. Processor State  $P_s$  is automatically entered when an interrupt is recognized other than one caused by a machine check or power failure.

- 4. Processor State  $P_4$  is entered whenever a machine check or power failure occurs.

Upon detection of interrupt the hardware initiates Processor State 3 or 4. It is the programs responsibility to determine what action is to be taken in any processor state.

| Organization<br>of Data               |                                                                                                                                                                                                                                                          | owing definitions<br>70/45 Processor                                       | describe the vari                                                                                                         | ous levels of da                                                       | ta organiza-                                |  |  |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|

|                                       | Bit — A<br>or one.                                                                                                                                                                                                                                       | bit is a single                                                            | binary digit havin                                                                                                        | ng the value of                                                        | either zero                                 |  |  |  |  |  |  |

|                                       | Byte —                                                                                                                                                                                                                                                   | A byte consists o                                                          | f eight informatio                                                                                                        | n bits.                                                                |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          |                                                                            | consists of two o<br>that is a multiple                                                                                   |                                                                        | s beginning                                 |  |  |  |  |  |  |

|                                       | Word — A word consists of four consecutive bytes beginning main memory location that is a multiple of four.                                                                                                                                              |                                                                            |                                                                                                                           |                                                                        |                                             |  |  |  |  |  |  |

|                                       | Doubleword — A doubleword consists of eight consecutive byter<br>ginning on a main memory location that is a multiple of eight.                                                                                                                          |                                                                            |                                                                                                                           |                                                                        |                                             |  |  |  |  |  |  |

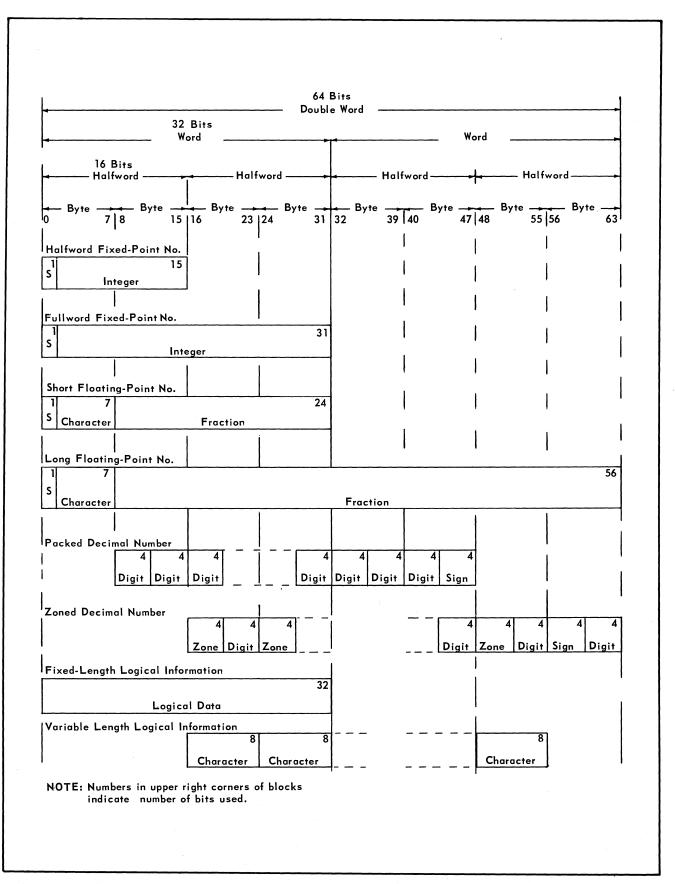

| Data Formats                          | • The basic unit of information in the $70/45$ Processor is a byte, which is the smallest addressable unit.                                                                                                                                              |                                                                            |                                                                                                                           |                                                                        |                                             |  |  |  |  |  |  |

|                                       | The internal code representation in the 70/45 is either the Extended<br>Binary-Coded-Decimal Interchange Code (EBCDIC) or the American<br>Standard Code for Information Interchange (ASCII) as specified by<br>program. (See Appendices A, B, C, and D.) |                                                                            |                                                                                                                           |                                                                        |                                             |  |  |  |  |  |  |

|                                       | There a<br>in Figure 1                                                                                                                                                                                                                                   |                                                                            | formats for data                                                                                                          | in main memor                                                          | ry as shown                                 |  |  |  |  |  |  |

| Numbering Systems                     | addresses in<br>16. The fir<br>through nin<br>letters A th                                                                                                                                                                                               | n the 70/45 Proc<br>st ten marks ar<br>ne (9); marks el<br>hrough F. Table | ng system is used<br>essor. The hexade<br>e represented by<br>leven through fift<br>2 illustrates the<br>umbers zero thro | ccimal system h<br>decimal numbe<br>een are represe<br>decimal, binary | as a base of<br>rs zero (0)<br>ented by the |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | Table 2. Basi                                                              | c Hexadecimal Ma                                                                                                          | rking System                                                           |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | Hexadecimal<br>(Base 16)                                                   | Bingry<br>(Base 2)                                                                                                        | Decimal<br>(Base 10)                                                   |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 0                                                                          | 0000                                                                                                                      | 0                                                                      | 1                                           |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 1                                                                          | 0001                                                                                                                      | 1                                                                      |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 2                                                                          | 0010                                                                                                                      | 2                                                                      |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 3                                                                          | 0011                                                                                                                      | 3                                                                      |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 4                                                                          | 0100                                                                                                                      | 4                                                                      |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 5                                                                          | 0101                                                                                                                      | 5                                                                      |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 6                                                                          | 0110                                                                                                                      | 6                                                                      |                                             |  |  |  |  |  |  |

| · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                                                          | 7                                                                          | 0111                                                                                                                      | 7                                                                      |                                             |  |  |  |  |  |  |

|                                       | 8 1000 8                                                                                                                                                                                                                                                 |                                                                            |                                                                                                                           |                                                                        |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | 9                                                                          | 1001                                                                                                                      | 9                                                                      |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | A                                                                          | 1010                                                                                                                      | 10                                                                     |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | B                                                                          | 1011                                                                                                                      | 11                                                                     |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | C                                                                          | 1100                                                                                                                      | 12                                                                     |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | D                                                                          | 1101                                                                                                                      | 13                                                                     |                                             |  |  |  |  |  |  |

|                                       |                                                                                                                                                                                                                                                          | E                                                                          | 1110                                                                                                                      | 14                                                                     |                                             |  |  |  |  |  |  |

|                                       | 1                                                                                                                                                                                                                                                        | F                                                                          | 1111                                                                                                                      | 15                                                                     | 1                                           |  |  |  |  |  |  |

## Description

Figure 1. Data Formats

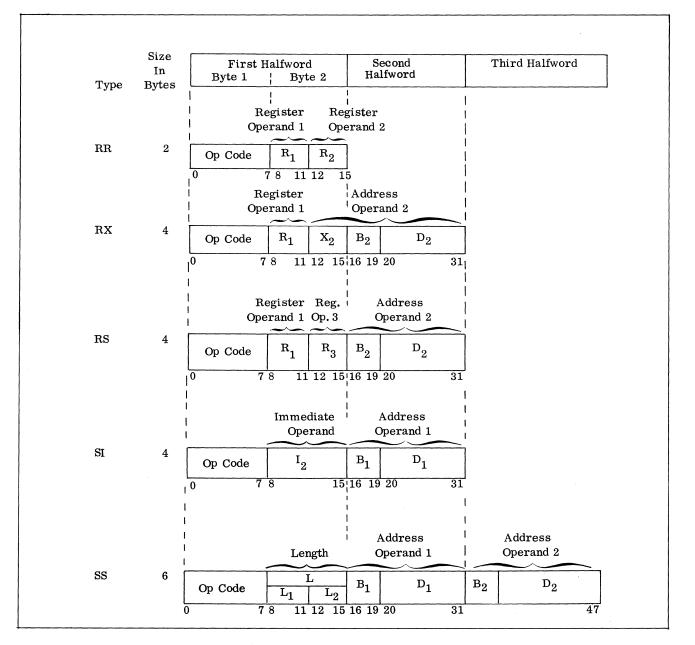

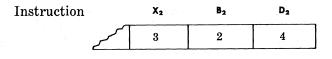

#### Instructions

◆ There are five basic instruction formats which express, in general terms, the operations to be performed. These instructions are:

- 1. RR = register—register operation.

- 2. RX = register—indexed storage operation.

- 3. RS = register—storage operation.

- 4. SI = storage----immediate operand operation.

- 5. SS = storage—storage operation.

The detailed format of each instruction is shown in Figure 2, and the instruction sub-fields are defined as follows:

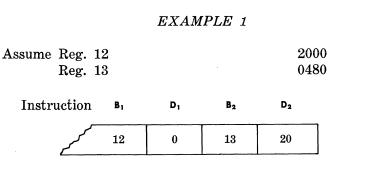

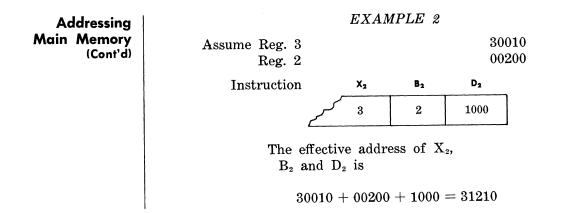

Addressing Main Memory ◆ The effective storage address is computed from the following binary components:

- 1. Base (contents of the designated base register,  $B_1$  or  $B_2$ )

- 2. Displacement  $(D_1, D_2)$

- 3. Index (contents of the designated index register,  $X_2$ ) for RX instructions.

In computing the address, the base and index are treated as unsigned 18-bit positive binary integers in bits 14-31 of the designated register. The displacement is treated as a 12-bit positive binary integer. The effective address is computed by adding the components as binary numbers, ignoring overflow.

Note: If register 0 is specified as the base register and/or the index register, then a zero quantity is to be added, *regardless* of the contents of register 0.

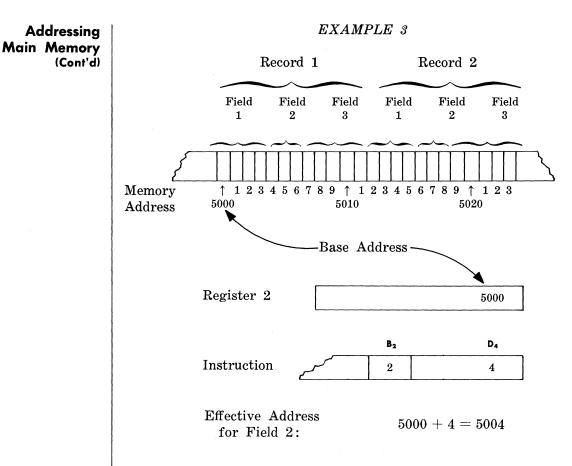

The following examples use decimal addresses for convenience:

The effective address of  $B_1$ ,  $D_1$  is 2000 The effective address of  $B_2$ ,  $D_2$  is 0500

Figure 2. 70/45 Instruction Formats

To process Record 2, the contents of Register 2 are increased by 12, the size of Record 1. The instruction field in (example 3) would then refer to Field 2 of Record 2.

If the instruction is an index-type instruction, a second general-purpose register, called an index register, is also used to generate the address. In example 3, the index register (Register 3) would initially be cleared to zero. After the first record is processed, the contents of Register 3 are increased by the record size. Then the instructions using Registers 2 and 3 for addressing would refer to Record 2. An illustration of this follows:

Register 2 (base)

Register 3 (index)

12

5000

Effective Address for Field 2, Record 2: 5000 + 12 + 4 = 5016

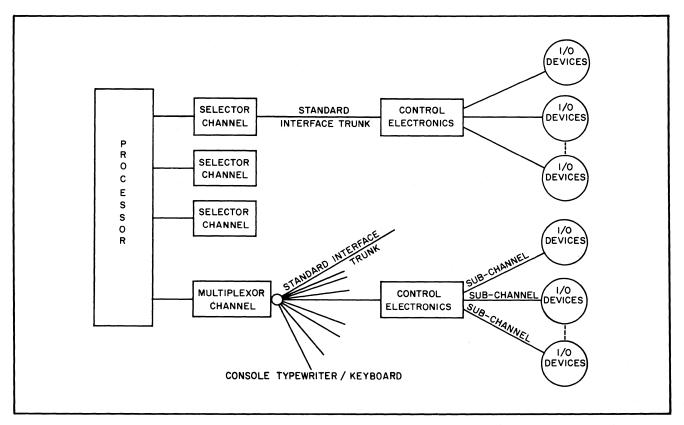

## Input/Output Channels

• The Model 70/45 Processor has two types of input/output channels, selector channels and a multiplexor channel.

Selector Channels — Up to three selector channels (optional) can be attached to a Model 70/45 Processor. Each selector channel can address up to 256 peripheral devices.

Each selector channel has two standard interface trunks and each standard interface trunk can be connected to the control electronics of an input/output device. A device control electronics controls one device (i.e., Card Reader, Printer), or a number of devices (i.e., Tape Controller: up to 16 Tape Stations).

Only one device can operate on a selector channel at one time. However, all selector channels can operate simultaneously with, and independently of, normal processor operation.

Multiplexor Channel — The multiplexor channel is standard on the Model 70/45 Processors, and can address up to 256 devices.

The multiplexor channel has eight standard interface trunks, each of which can be connected to a device control electronics. This permits the multiplexor channel to operate devices on all eight trunks simultaneously. The limit as to the number of input/output devices that can be connected is determined by the device control electronics. A ninth trunk is provided on the multiplexor channel for exclusive use by the Model 70/97 Console.

Figure 3 depicts the logical connection of the I/O channels and I/O devices.

Figure 3. 70/45 Input/Output Flow

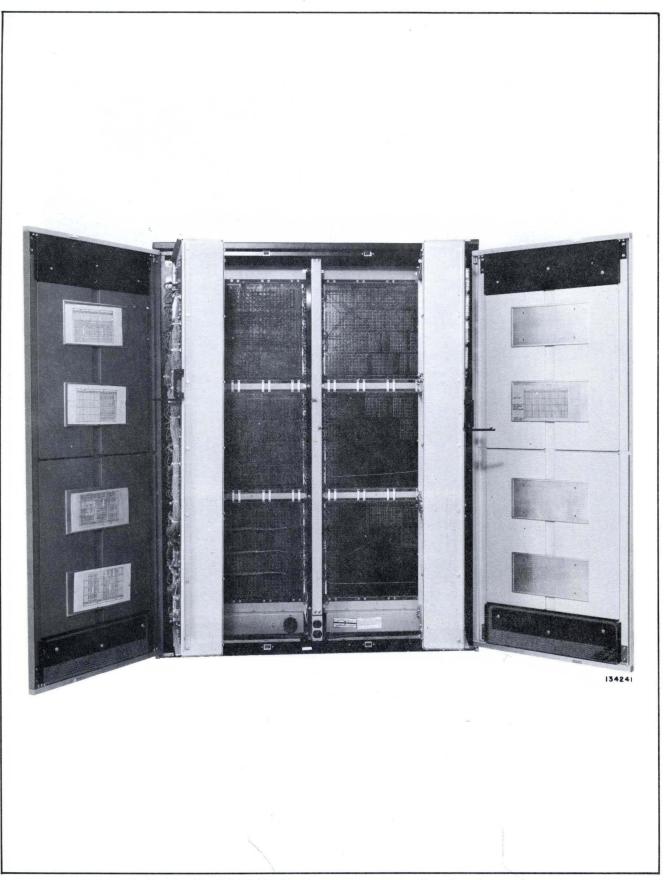

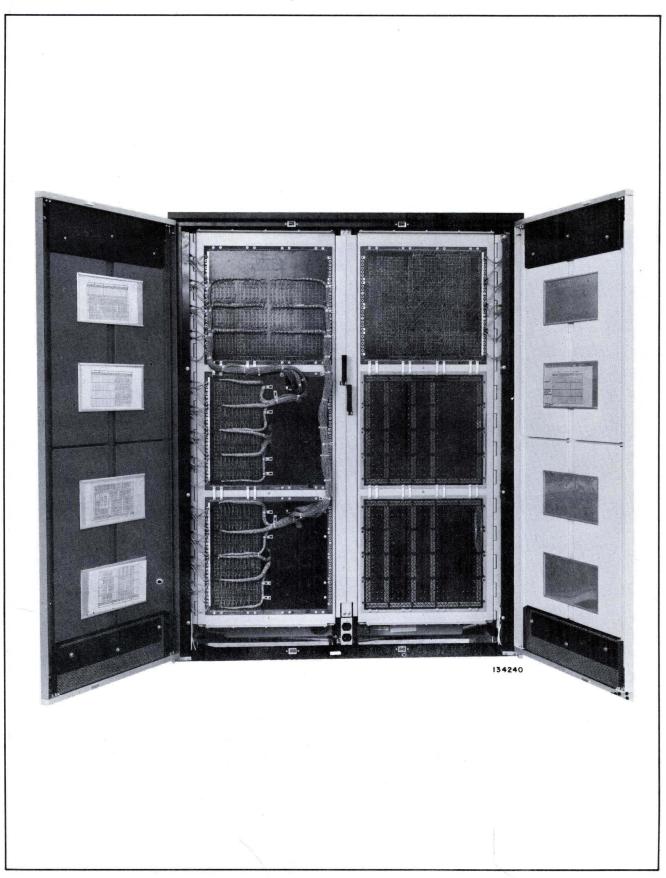

| SUB-UNITS                 |                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |                                  |                               |                                |                                                                                                                                                                                                                                                            |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------|-------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Basic Processing Unit     | to an intern<br>perform ari<br>and perforn                                                                                                                                                                                                                                                                                                                                                                        | nally<br>thme<br>n br         | store<br>tic op<br>anchi         | ed pi<br>perati<br>ing o      | rogra<br>ions,<br>operat       | BPU) (See Figures 4 and 5), in response<br>m, can effect internal data transmission,<br>execute decisions and control instructions,<br>cions. In addition, the BPU can operate<br>input or an output mode.                                                 |  |  |  |  |

| Main Memory               | available in<br>time is 1.44<br>main memo<br>storage. The                                                                                                                                                                                                                                                                                                                                                         | the<br>micr<br>ry to<br>e pro | expa<br>oseco<br>b the<br>ocesso | ndabl<br>nds.<br>mer<br>or no | e siz<br>This<br>nory<br>rmall | of expandable magnetic core storage and is<br>es as indicated in Table 1. Memory-cycle<br>is the time to transfer two bytes from the<br>register and to regenerate the bytes in<br>y operates on two 8-bit bytes at a time,<br>able data unit is one byte. |  |  |  |  |

| Non-Addressable<br>Memory | ◆ This memory is a portion of the main memory that cannot be addressed<br>by program. A set of registers that services the devices attached to a<br>multiplexor channel is contained in the non-addressable main memory.<br>The size of this memory will vary in accordance with the capacity of the<br>main memory selected. Non-addressable memory is in addition to the main<br>memory capacity of the system. |                               |                                  |                               |                                |                                                                                                                                                                                                                                                            |  |  |  |  |

| Fast Memory               | • The fast memory is a micromagnetic storage device consisting of 128 four-byte words, the cycle time of which is 300 nanoseconds. Each word in a fast memory is uniquely addressed.                                                                                                                                                                                                                              |                               |                                  |                               |                                |                                                                                                                                                                                                                                                            |  |  |  |  |

|                           | The follo<br>Processor.                                                                                                                                                                                                                                                                                                                                                                                           | wing                          | ; regi                           | sters                         | are                            | contained in the fast memory of a $70/45$                                                                                                                                                                                                                  |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                   | ers a                         | ire us                           | sed by                        |                                | rs — All locations designated as processor<br>processor for program control and cannot                                                                                                                                                                     |  |  |  |  |

|                           | each process                                                                                                                                                                                                                                                                                                                                                                                                      | or st                         | tate.                            | Thes                          | e reg                          | se locations are the general registers for<br>isters are used by the program for base<br>r storing operands.                                                                                                                                               |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                   | -                             |                                  |                               |                                | s — An Interrupt Mask register for each<br>bits 32 interrupt conditions.                                                                                                                                                                                   |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |                                  |                               |                                |                                                                                                                                                                                                                                                            |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                   | P <sub>1</sub>                | P <sub>2</sub>                   | P <sub>3</sub>                | P4                             |                                                                                                                                                                                                                                                            |  |  |  |  |

|                           | Interrupt<br>Mask                                                                                                                                                                                                                                                                                                                                                                                                 | 40                            | 44                               | 50                            | 14                             | See Interrupt Flags                                                                                                                                                                                                                                        |  |  |  |  |

|                           | L                                                                                                                                                                                                                                                                                                                                                                                                                 | <b></b>                       | i <b>l</b>                       | L                             | <b>.</b>                       | L                                                                                                                                                                                                                                                          |  |  |  |  |

Figure 4. Interior Model 70/45 Processor (Rear View Showing Frame Opened)

Figure 5. Interior Model 70/45 Processor (Rear View Showing Frame Closed)

#### Fast Memory (Cont'd)

4. Interrupt Status Registers — An Interrupt Status register for each processor state stores interrupt identification information and operational control information. This register contains indications of the last state interrupted, the protection key, the decimal mode (ASCII or EBCDIC), the privileged mode bit and the supervisor call identification.

|                    | P <sub>1</sub> | P <sub>2</sub> | P3 | P4 |     |    |     |    |   |    |    |      |

|--------------------|----------------|----------------|----|----|-----|----|-----|----|---|----|----|------|

|                    |                |                |    |    | Di  | 20 | DR  | 21 | D | R2 | DR | 3    |

| Interrupt          |                |                |    |    | ISI | 0  | KEY | A  | 0 | 0  |    | ·    |

| Status<br>Register | 41             | 45             | 51 | 15 | ISI | 0  | KEY | 0  | 0 | 0  |    | LL – |

| Register           |                |                |    |    | ISI | 0  | KEY | 0  | 0 | 0  |    | - 11 |

|                    |                |                |    |    | 0   | 0  | KEY | N  | 0 | 0  |    |      |

|                    |                |                |    |    | L   | L  |     |    |   | A  | 4t |      |

5. *Program Counter* — A Program Counter for each processor state contains the main memory address of the next instruction to be executed, the condition code and the instruction length code of the last instruction in which an interrupt occurred, and the program mask.

|              | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> | P4    |                 |                                |

|--------------|----------------|----------------|----------------|-------|-----------------|--------------------------------|

|              |                |                |                |       | DRO DR1 DR2 DR3 |                                |

|              |                |                |                |       | ILC Sig<br>Err  |                                |

|              | 42 46          | 46             | 59             | 52 16 | 16              | ILC Exp<br>Und DDOGDAN GOUNTED |

| P — Register |                | 52             | 10             |       |                 | 10                             |

|              |                |                |                |       | CC FP<br>Ov     |                                |

|              |                |                |                |       |                 |                                |

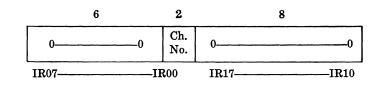

6. Input/Output Channel Registers — A set of four registers for each selector channel controls input/output operation. A set of four registers for the multiplexor channel controls initiation and termination of input/ output operations on the multiplexor channel.

# Fast Memory (Cont'd)

7. Floating-Point Registers — Four floating-point registers (each is two words long) are used in floating-point arithmetic.

|                           | MUX | SEL1 | SEL2 | SEL3 | I/O Channel Registers                                                                                                                                                                                                       |

|---------------------------|-----|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assembly<br>and<br>Status | 25  | 35   | 65   | 75   | DR0<br>DR1<br>DR2AssyMan. Req.Dev. EndInt. Pend.Sec. Ind.Dev. BusyDev. Inop.Cont. BusyStat. Mod.                                                                                                                            |

| CCR 1                     | 24  | 34   | 64   | 74   | DR0     DR1     DR2     DR3       0     0     0     0     0       0     0     0     0     0       0     0     0     0     0       0     0     0     0     0       0     0     0     0     0       0     0     0     0     0 |

| CCR 2                     | 23  | 33   | 63   | 73   | DR0DR1DR2DR3CDPCIPCICh.<br>Data                                                                                                                                                                                             |

| C A R                     | 22  | 32   | 62   | 72   | DRO DR1 DR2 DR3 Device Address of next Number CCW                                                                                                                                                                           |

#### Fast Memory (Cont'd)

8. Interrupt Flag Register — One interrupt Flag register is provided. When an interrupt condition occurs, a bit associated with this condition is set in the Interrupt Flag register.

|                    |            | [  | DRO         | ]  |             |    | R1          | ]  |           | D  | R2         | ]  |           | D  | R3          |    |

|--------------------|------------|----|-------------|----|-------------|----|-------------|----|-----------|----|------------|----|-----------|----|-------------|----|

|                    | Tes<br>Moo |    | Sig.<br>Err |    | Add<br>Err  |    | Not<br>Spe  |    | MU        | x  | SEI<br>#3  |    | EX'<br>#6 | г. | EX1<br>#2   | г. |

|                    |            | 7C |             | 6C |             | 5C |             | 4C |           | 3C |            | 2C |           | 1C |             | С  |

|                    | F.P<br>Ov. | -  | Div<br>Err  | -  | Op.<br>Tra  |    | Not<br>Spe  |    | SEI<br>#6 |    | SEI<br>#2  | ь. | EX'<br>#5 | Г. | EX'<br>#1   | Г. |

| Interrupt<br>Flags |            | 78 |             | 68 |             | 58 |             | 48 |           | 32 |            | 28 |           | 18 |             | 8  |

| (43)               | Dec<br>Ov. | •  | Exp<br>Ov.  | ). | Priv<br>Op. | -  | Con<br>Int. |    | SEI<br>#5 | ٦. | SEI<br>#1  |    | SEI<br>#4 | J. | Mac<br>Che  |    |

|                    |            | 74 |             | 64 |             | 54 |             | 44 |           | 34 |            | 24 |           | 14 |             | 4  |

|                    | Exp<br>Und |    | Dat<br>Err  |    | Sup<br>Call |    | ETC         | 5  | SEI<br>#4 | 4. | Not<br>Spe |    | EX7<br>#3 | Г. | Pow<br>Fail | _  |

|                    |            | 70 |             | 60 |             | 50 |             | 40 |           | 30 |            | 20 |           | 10 |             | 0  |

## **Read-Only Memory**

• Read-Only Memory (ROM) is an integral part of the 70/45 Processor. The standard 70/45 ROM consists of two banks of 1,024 54-bit words each. Each word contains one microinstruction of 53-bit length. In addition, the 70/45 ROM contains a 12-bit address register.

The wired-in microprogram logic contained in the read-only memory banks control the elementary operations of the 70/45. The cycle time of one ROM bank is 960 nanoseconds. The effective cycle time of both ROM banks operating alternately is 480 nanoseconds with a 54-bit access.

The 70/45 Processor is obtainable with two additional ROM banks containing the microinstructions for any combination of the available Emulator features. (Refer to Optional Features.)

## Program Control and Arithmetic Unit

♦ The program control and arithmetic unit in the Model 70/45 Processors interprets and executes the instructions stored in main memory. Registers and indicators monitor the sequence of operations, perform automatic accuracy checks, and communicate with the RCA standard interface in the control of input/output devices.

## **Operator's Console**

◆ The Model 70/97 Operator's Console is a free standing, self-contained unit which consists of two portions: the Console Typewriter and the Operator's Console/Display Panel, mounted together on a Console table. (See Figure 6.) The console panel provides the controls and indicators to enable system operation in conjunction with operating system programs. The operator has complete control of the system and communicates with the system via a set of control switches and the console typewriter.

Figure 6. Operator's Console (Model 70/97)

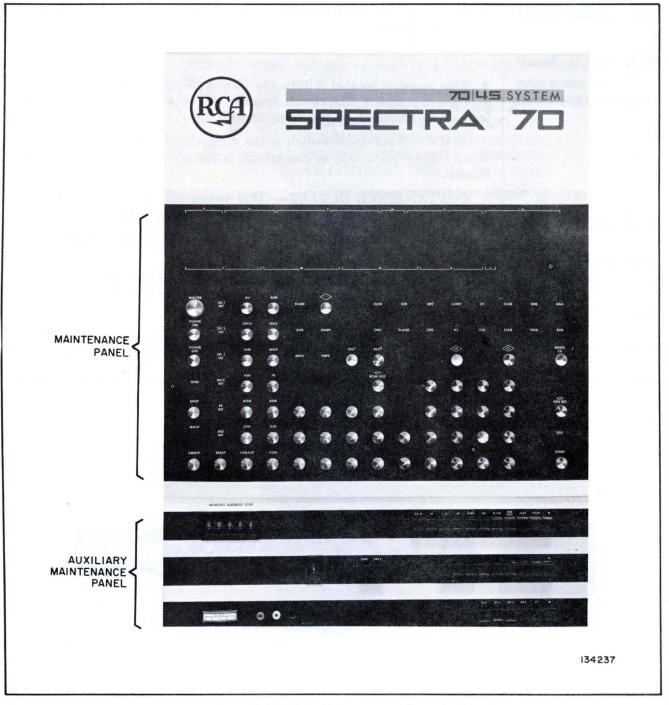

## Maintenance Console Panel

• The Maintenance Console for the 70/45 Processor consists of two panels: the Maintenance Panel and the Auxiliary Maintenance Panel. These two panels are physically mounted on the power supply rack and incorporate controls and indicators to enable system operation without the assistance of operating system programs for maintenance purposes. Refer to Tables 4 and 5 for description and functions of the indicators and controls of these panels. (See Figure 7.)

Power Supply

# CONTROLS AND INDICATORS

• The following describes the operational functions of the circuit breakers, pushbutton and indicators that comprise operator's controls for the 70/45 Processor.

Control Panel and the AC Input and Distribution Panel.

$\bullet$  The 70/45 Processor Power Supply furnishes power to the Basic

Processing Unit and to the High-Speed Memory in addition to the Operator's Console. Contained within the Power Supply rack are the Typing Control and Power Supply electronics. Refer below for description and functions of the Controls and Indicators provided on the Power Supply

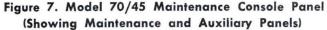

Power Supply Panels AC INPUT AND DISTRIBUTION PANEL

◆ This panel is located within the Power Supply cabinet and is shown in Figures 8 and 9. The circuit breaker switches provide AC power protections as indicated on the front panel.

MAIN — This on-off switch is the main circuit breaker for ac power. When this switch is ON, ac line voltage is available to the Processor Power Supply.

CONVENIENCE OUTLET — This switch provides ac line voltage to the convenience outlets located in the power supply racks.

FANS — This switch provides ac line voltage to the fans located within the various processor racks.

*CONTROLS* — This switch provides ac line voltage protections to the thermostat warning signal controls located in the Power Supply and Basic Processor Unit racks.

-5; +30/+20/+10; +50/+5/-30 — These circuit breakers protect the individual power supply voltages as supplied throughout the processor.

Figure 8. AC Input and Distribution Panel

Figure 9. Power Supply and Control Electronics Rack (Rear View)

### POWER SUPPLY CONTROL PANEL

◆ This panel is located within the Power Supply rack as shown in Figures 9 and 10. Essentially this panel is utilized for maintenance purposes. However, the functions of the controls and indicators pertaining to this panel are described herein, as an aid to the operating personnel.

TEST — This switch is used to turn on the DC power in the test mode. The DC power is isolated from the logic rack(s). Pressing the pushbutton will light its associated indicator.

*RESET* — Pressing this pushbutton will reset all of the power supply sensing functions. The indicator is lit after a fault is detected and will go off after the POWER SUPPLY is reset.

CURRENT OVERLOAD — These indicators will light whenever a specific current overload (as noted on the panel) is detected in the power supply input.

VOLTAGE OUT OF TOL — When the OPERATE and/or TURN ON indicators are displayed, the indication is that the protection circuits have detected a voltage error.

*VOLTMETER* — This nine position rotary switch and its associated test jacks, are used for monitoring the output voltage as determined by the positioning of the switch.

TEMP. WARNING IN FRAME — When indicator is lit, a temperature sensor is approaching the maximum safe limits. The location of the sensor is as identified by the markings on the panel.

TEMP. OVERHEAT IN FRAME AND TEMP. OVERHEAT IN COOLER — The indicator associated with the sensor when lit, indicates an overheating condition. The location of the sensor is as identified by the markings on the panel.

LAMP TEST — Pressing this button will cause all Control Panel lamps to light, thus enabling the identification of any defective bulb.

Figure 10. Power Supply Control Panel

## Operator's Console Display Panel

♦ By means of the three Digi-Switches and pushbuttons, an operator can perform an initial program load function from any input device; start and stop the computer; or interrupt the program in order to initiate communication with the software via the typewriter. The following listing describes the type and use of the various switches and indicators that comprise the Operator's Display Panel. (See Figure 11 and Table 3.)

Figure 11. Model 70/97 Operator's Console Display Panel

| Table | 3. | <b>Operator's</b> | Console | Panel | (Indicators | and | Controls) |

|-------|----|-------------------|---------|-------|-------------|-----|-----------|

|       |    |                   |         |       |             |     |           |

(Reference Fig. 11)

| Panel Designation                               | Туре                                       | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Load Unit Switches<br>(No markings on<br>panel) | Digi-Switches                              | The three digi-switches provide for the entry of the I/O chan-<br>nel and device number for initial program load function and<br>are used in conjunction with the LOAD switch. All three<br>switches have sixteen positions labeled 0 through 9 and A<br>through F. Each switch is used as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                 |                                            | a. Switch 1<br>This (leftmost) switch provides the three bit channel ad-<br>dress of which only positions 0 through 7 are used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                 |                                            | b. Switch 2<br>This (center) switch provides the 4 high order bits of the<br>device number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                                 |                                            | c. Switch 3<br>This (rightmost) switch provides the 4 low order bits of the<br>device number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| MASTER                                          | Pushbutton Switch/<br>Indicator<br>(Green) | This alternate action switch is used to enable the power supply<br>control circuits and must be in the ON condition before the<br>POWER ON switch at the Maintenance Panel can be activated.<br>This switch can also be used as an emergency power off switch,<br>in which case DC power is disconnected, by-passing the normal<br>DC power off sequencing, and causing the power failure inter-<br>rupt to be set in the processor. The indicator is turned on upon<br>the pressing of this switch, and remains on, until the switch is<br>pressed again to turn off power. Whenever this switch is in its<br>OFF condition, the POWER ON on the Maintenance Panel is<br>ineffective. This switch does not control power to the console<br>typewriter (See Note 1). |  |  |  |

| POWER<br>READY                                  | Indicator<br>(Green)                       | This indicator is turned on to indicate that the processor DC<br>power is on and that the processor is ready for operation. This<br>occurs when the processor power sequencing is completed and<br>remains on until power is removed from the processor, either at<br>the completion of power off sequencing, or emergency power<br>off procedures.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| IDLE                                            | Indicator<br>(Yellow/Red Border)           | This indicator is turned on when the Idle instruction is oper-<br>ating. (See Note 2.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| OVER HEAT                                       | Indicator<br>(Red)                         | This indicator is turned on whenever the temperature in the processor exceeds its environmental design. (See Note 2.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| LOCAL                                           | Indicator<br>(Yellow)                      | This indicator is turned on whenever the Console typewriter<br>LOCAL-OFF-LINE switch is positioned to LOCAL, or when<br>DC power is off in the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| ERROR                                           | Indicator<br>(Red)                         | This indicator is turned on whenever the following errors have<br>been detected in the processor:MPPEIOPEMMPEROMEFMPEPEINT (During load operation)The particular error which has been detected can be determined<br>from the specific indicators on the Maintenance Panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

# Table 3. Operator's Console Panel (Indicators and Controls) (Cont'd)

(Reference Fig. 11)

| Panel Designation                            | Туре                                        | Description and Function                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                          |                                                 |  |  |

|----------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| SEND                                         | Indicator<br>(Yellow/Red Border)            | from the Console typever a read typewrin                                                                                                                                                                                                                                                      | Vhen lit, indicates that the Processor is ready to receive input<br>rom the Console typewriter. The indicator is turned on when-<br>ver a read typewriter operation is initiated. The indicator is<br>urned off when either the EOT key or the Error key on the<br>eyboard is activated. |                                                 |  |  |

| P. S. 2 <sup>1</sup><br>P. S. 2 <sup>0</sup> | Indicators<br>(Yellow)                      | Displays the curren halted as follows:                                                                                                                                                                                                                                                        | t program state w                                                                                                                                                                                                                                                                        | when the processor is                           |  |  |

|                                              |                                             | P.S. 2 <sup>1</sup>                                                                                                                                                                                                                                                                           | P.S. 2 <sup>0</sup>                                                                                                                                                                                                                                                                      | Program State                                   |  |  |

|                                              |                                             | 0                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                        | 4                                               |  |  |

|                                              |                                             | 0                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                        | 3                                               |  |  |

|                                              |                                             | 1                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                        | 2                                               |  |  |